- 您现在的位置:买卖IC网 > Sheet目录3861 > PIC18F45K80-I/ML (Microchip Technology)MCU PIC 32KB FLASH 44QFN

2010-2012 Microchip Technology Inc.

DS39977F-page 169

PIC18F66K80 FAMILY

10.9

Context Saving During Interrupts

During interrupts, the return PC address is saved on

the stack. Additionally, the WREG, STATUS and BSR

registers are saved on the Fast Return Stack.

If a fast return from interrupt is not used (see

), the user

may need to save the WREG, STATUS and BSR regis-

ters on entry to the Interrupt Service Routine (ISR).

Depending on the user’s application, other registers

also may need to be saved.

Example 10-1 saves and restores the WREG, STATUS

and BSR registers during an Interrupt Service Routine.

EXAMPLE 10-1:

SAVING STATUS, WREG AND BSR REGISTERS IN RAM

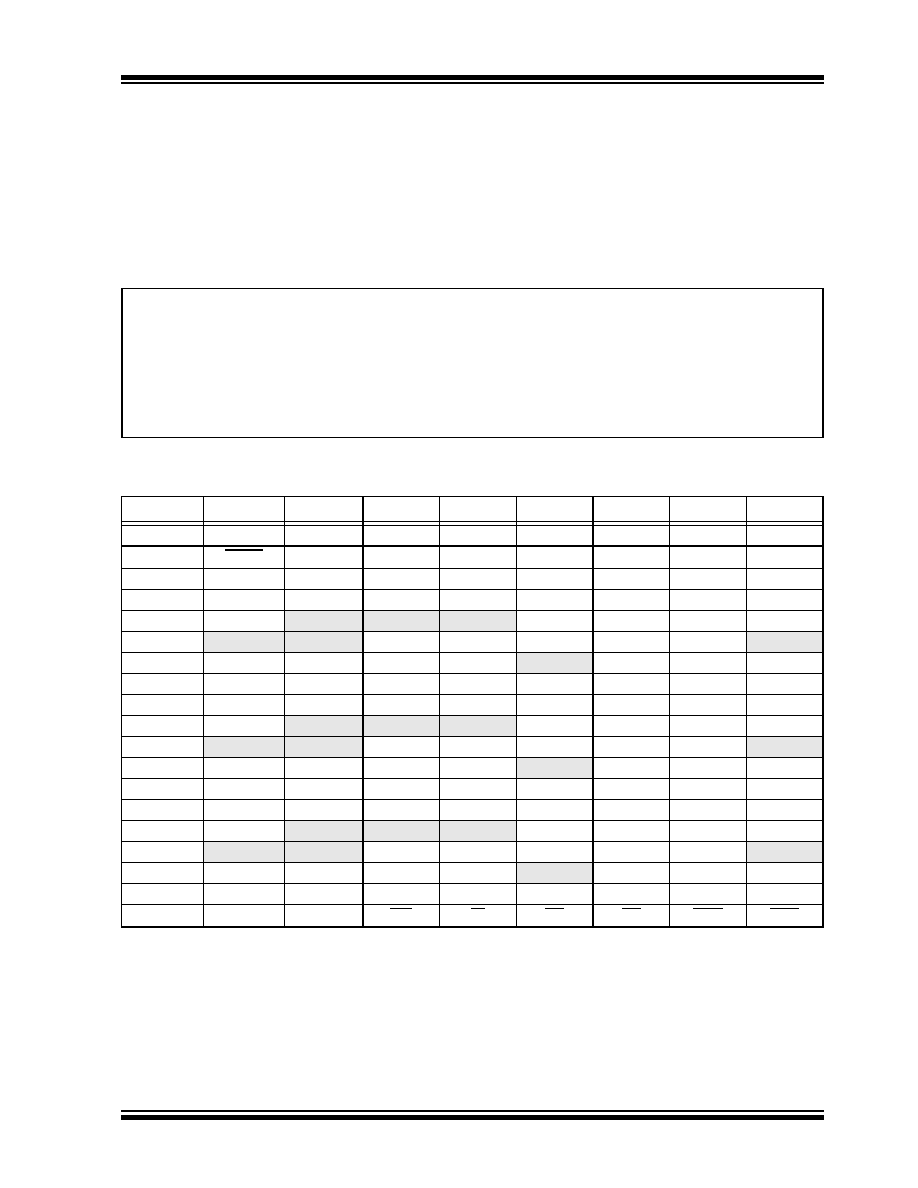

TABLE 10-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

INTCON

GIE/GIEH

PEIE/GIEL

TMR0IE

INT0IE

RBIE

TMR0IF

INT0IF

RBIF

INTCON2

RBPU

INTEDG0

INTEDG1

INTEDG2

INTEDG3

TMR0IP

INT3IP

RBIP

INTCON3

INT2IP

INT1IP

INT3IE

INT2IE

INT1IE

INT3IF

INT2IF

INT1IF

PIR1

PSPIP

ADIF

RC1IF

TX1IF

SSPIF

TMR1GIF

TMR2IF

TMR1IF

PIR2

OSCFIF

—

BCLIF

HLVDIF

TMR3IF

TMR3GIF

PIR3

—

RC2IF

TX2IF

CTMUIF

CCP2IF

CCP1IF

—

PIR4

TMR4IF

EEIF

CMP2IF

CMP1IF

—

CCP5IF

CCP4IF

CCP3IF

PIR5

IRXIF

WAKIF

ERRIF

TXB2IF

TXB1IF

TXB0IF

RXB1IF

RXB0IF

PIE1

PSPIE

ADIE

RC1IE

TX1IE

SSPIE

TMR1GIE

TMR2IE

TMR1IE

PIE2

OSCFIE

—

BCLIE

HLVDIE

TMR3IE

TMR3GIE

PIE3

—

RC2IE

TX2IE

CTMUIE

CCP2IE

CCP1IE

—

PIE4

TMR4IE

EEIE

CCP2IE

CMP1IE

—

CCP5IE

CCP4IE

CCP3IE

PIE5

IRXIE

WAKIE

ERRIE

TXB2IE

TXB1IE

TXB0IE

RXB1IE

RXB0IE

IPR1

PSPIP

ADIP

RC1IP

TX1IP

SSPIP

TMR1GIP

TMR2IP

TMR1IP

IPR2

OSCFIP

—

BCLIP

HLVDIP

TMR3IP

TMR3GIP

IPR3

—

RC2IP

TX2IP

CTMUIP

CCP2IP

CCP1IP

—

IPR4

TMR4IP

EEIP

CMP2IP

CMP1IP

—

CCP5IP

CCP4IP

CCP3IP

IPR5

IRXIP

WAKIP

ERRIP

TXB2IP

TXB1IP

TXB0IP

RXB1IP

RXB0IP

RCON

IPEN

SBOREN

CM

RI

TO

PD

POR

BOR

Legend:

Shaded cells are not used by the interrupts.

MOVWF

W_TEMP

; W_TEMP is in virtual bank

MOVFF

STATUS, STATUS_TEMP

; STATUS_TEMP located anywhere

MOVFF

BSR, BSR_TEMP

; BSR_TMEP located anywhere

;

; USER ISR CODE

;

MOVFF

BSR_TEMP, BSR

; Restore BSR

MOVF

W_TEMP, W

; Restore WREG

MOVFF

STATUS_TEMP, STATUS

; Restore STATUS

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F32KA302-I/ML

MCU 32KB FLASH 2KB RAM 28-QFN

PIC18LF45K80-I/ML

MCU PIC ECAN 32KBFLASH 44QFN

PIC18F4221-I/PT

IC PIC MCU FLASH 2KX16 44TQFP

PIC18F1320-I/SO

IC MCU FLASH 4KX16 A/D 18SOIC

PIC18LF2321-I/SS

IC PIC MCU FLASH 4KX16 28SSOP

PIC16F917-I/PT

IC PIC MCU FLASH 8KX14 44TQFP

PIC18F1320-I/SS

IC MCU FLASH 4KX16 A/D 20SSOP

PIC24FV32KA301-I/P

MCU 32KB FLASH 2KB RAM 20-PDIP

相关代理商/技术参数

PIC18F45K80-I/P

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80-I/PT

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80T-I/ML

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80T-I/PT

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT